School of Engineering THE COLLEGE OF NEW JERSEY

Fall Semester, 2003

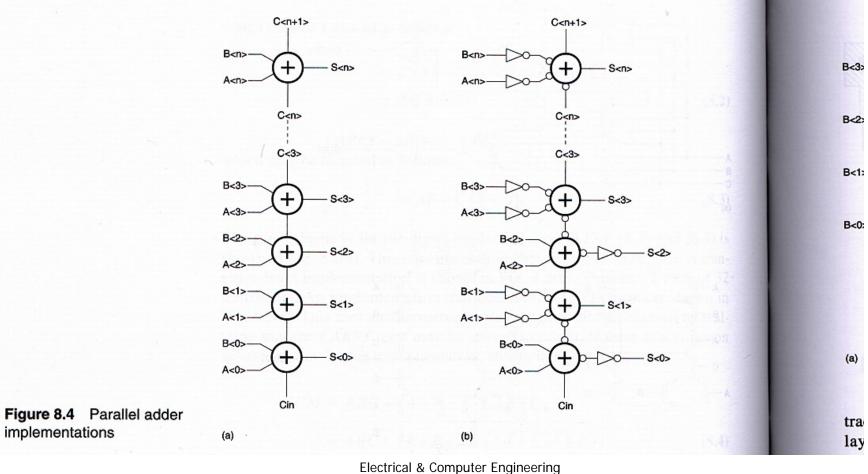

implementations

2

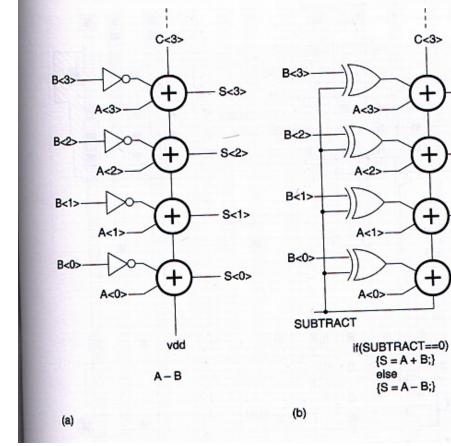

FIGURE 8.5 Arithmetic operators: (a) subtractor; (b) adder/subtractor

Electrical & Computer Engineering School of Engineering THE COLLEGE OF NEW JERSEY

S<3>

S<2>

S<1>

S<0>

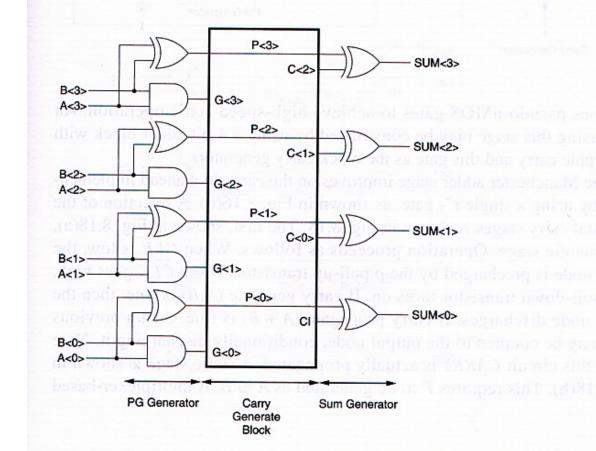

FIGURE 8.14 Generic carry-lookahead adder (CLA)

Electrical & Computer Engineering School of Engineering THE COLLEGE OF NEW JERSEY

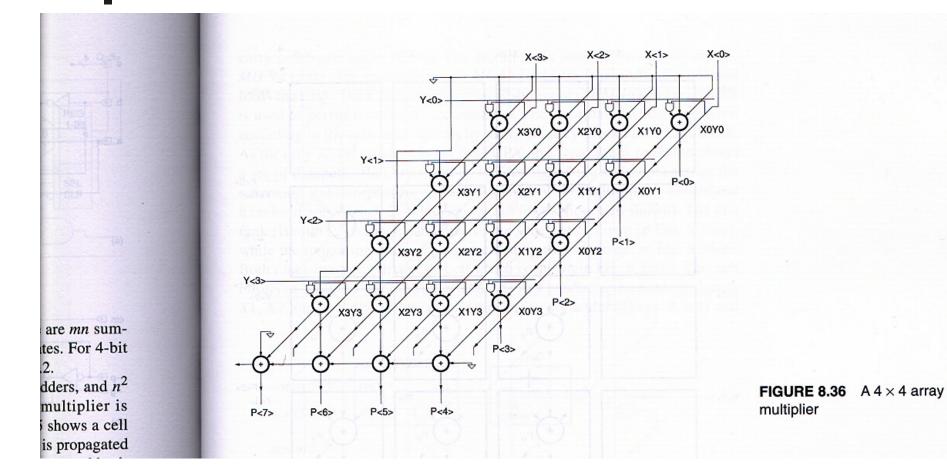

| TABLE 8.2 4-bit Multiplier Partial Products |      |            |         |              |              |              |          |                            |  |

|---------------------------------------------|------|------------|---------|--------------|--------------|--------------|----------|----------------------------|--|

|                                             | ets: | Line still | cu p) a | X3<br>Y3     | X2<br>Y2     | X1<br>Y1     | X0<br>Y0 | Multiplicand<br>Multiplier |  |

|                                             |      |            | X3Y1    | X3Y0<br>X2Y1 | X2Y0<br>X1Y1 | X1Y0<br>X0Y1 | X0Y0     |                            |  |

|                                             |      |            |         |              |              |              |          |                            |  |

|                                             |      | X3Y2       | X2Y2    | X1Y2         | X0Y2         |              |          |                            |  |

|                                             | X3Y3 | X2Y3       | X1Y3    | X0Y3         |              |              |          |                            |  |

| P7                                          | P6   | P5         | P4      | P3           | P2           | P1           | PO       | Product                    |  |

## m Out

## B first hat rs cation.

ial product is early with the

ultiplier stage ibed so far has ers of this type

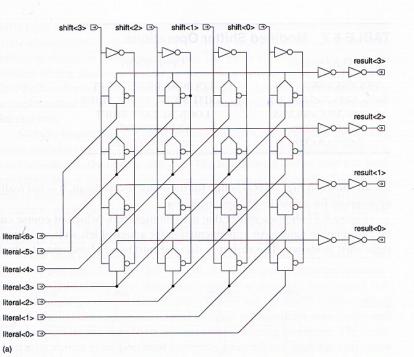

igns for arith-4-by-4 barrel tary transmis-(*literal*<6:0>) of the output

he literal bus. er on the front

vell as rotates. sion gate. The silicided poly e literal input. ble. While the

F

| TABLE 8.6 | Shifter Operations |  |  |  |

|-----------|--------------------|--|--|--|

| SHIFT     | RESULT             |  |  |  |

| 1         | LITERAL<3:0>       |  |  |  |

| 2         | LITERAL<4:1>       |  |  |  |

| 4         | LITERAL<5:2>       |  |  |  |

| 8         | LITERAL<6:3>       |  |  |  |

(b)

FIGURE 8.46 Array shifter using transmission gates: (a) circuit; (b) cell layout New Jersey

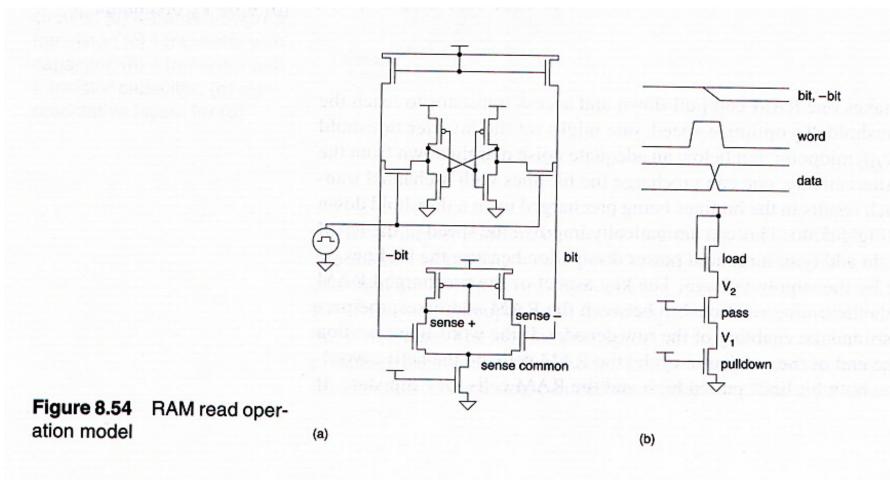

in driving the es to the RAM luring the read uit. In this cirw the data and serted (actually s driven to V<sub>SS</sub>,

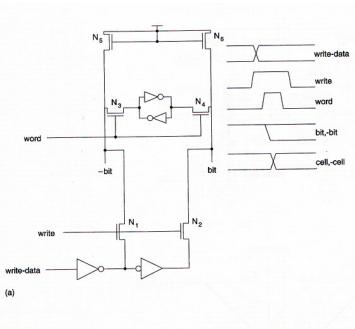

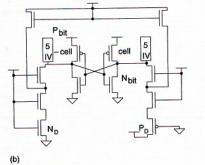

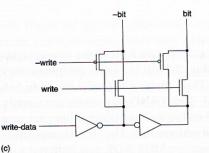

serted (actually s driven to  $V_{SS}$ , n V<sub>DD</sub>. Figure re shows a zero e written, node and at the same hreshold. In the he write-access P<sub>bit</sub> (the RAM N<sub>5</sub> (the bit-line ine side,  $P_D$ ,  $N_2$ write operations istors, as shown ver all process, ot of the wavemodel the RAM and -write-data

FIGURE 8.57 Static RAMwrite circuits: (a) n-channel pass transistors; (b) circuit model during write; (c) complementary transmission gate version ew Jersey

If the delay in Fig. 8.64 cou bit basis to enab be used where routed to a sens

the decoder has rite operation is being actively s. However, the nt values before AM, this speed y sizing transisdecode signal.

nd write ports. ng pass transis-

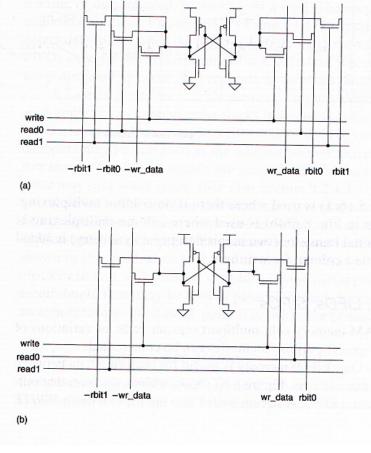

FIGURE 8.65 Multiported (2R-1W) RAM cell: (a) fully differential; (b) single-ended read