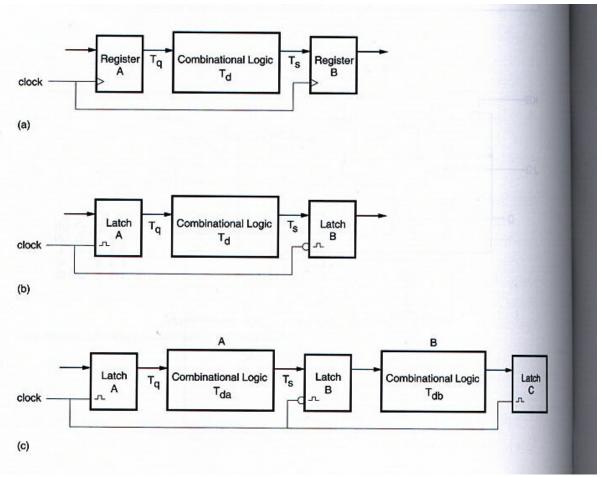

FIGURE 5.49 Pipelined system options: (a) a register based pipelined system; (b) a latch based pipelined system; (c) another example of a latch based pipeline system

Electrical & Computer Engineering

School of Engineering

THE COLLEGE OF NEW JERSEY

Electrical & Computer Engineering

School of Engineering

THE COLLEGE OF NEW JERSEY

Electrical & Computer Engineering

School of Engineering

THE COLLEGE OF NEW JERSEY

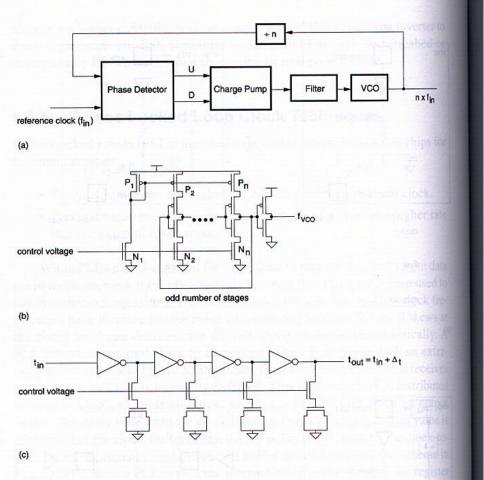

pump PLL: (a) basic PLL block diagram; (b) typical CMOS VCO circuit; (c) typical CMOS VCDL circuit

Electrical & Computer Engineering

School of Engineering

THE COLLEGE OF NEW JERSEY

Electrical & Computer Engineering

School of Engineering

THE COLLEGE OF NEW JERSEY

Electrical & Computer Engineering School of Engineering THE COLLEGE OF NEW JERSEY

Electrical & Computer Engineering

School of Engineering

THE COLLEGE OF NEW JERSEY

Electrical & Computer Engineering School of Engineering THE COLLEGE OF NEW JERSEY

Electrical & Computer Engineering

School of Engineering

THE COLLEGE OF NEW JERSEY